Projekte

Low-cost 400Mbit/s Serial-Link

FPGAs im mittlerer und hohen Preis-/Leistungssegment verfügen heute in der Regel über serielle Transceiver mit Übertragungsrate von mehreren Gbit/s. Bei diesen Transceivern wird das zum Lesen der Daten notwendige Taktsignal z.B. mittels einer PLL aus dem Datenstrom rekonstruiert. Dadurch kann auf eine dedizierte Taktleitung verzichtet werden, was die Übertragung über längere Strecken stark vereinfacht. Stehen Transceiver z.B. aus Kostengründen nicht zur Verfügung, muss auf alternative Ansätze ausgewichen werden.

Im Rahmen dieses Projekts wurde eine serielle Datenverbindung mit eingebettetem Taktsignal auf Basis eines Lattice ECP5-FPGAs ohne Transceiver realisiert. Die Module zur Taktrückgewinnung, 8B/10B-Datenkodierung und Fehlererkennung wurden in der programmierbaren Logik umgesetzt, was eine zukünftige Portierung auf andere FPGA-Varianten ermöglicht. Auf physikalischer Ebene wurde eine direkte LVDS-Verbindungen über ein einfaches Flachbandkabel mit einer Länge von 50 cm realisiert.

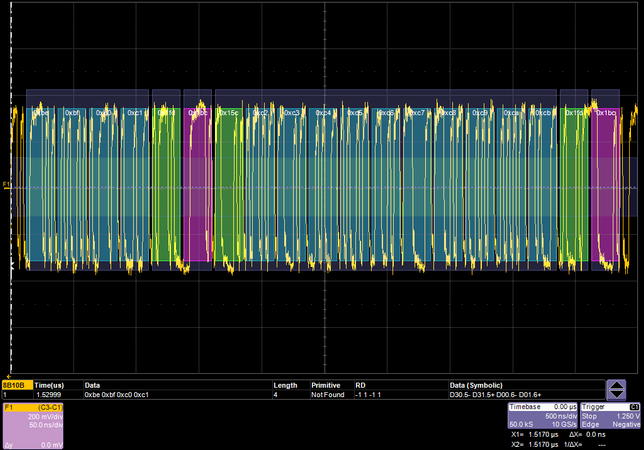

In der beschriebenen Implementierung konnte eine stabile Datenverbindung mit einer Datenrate von 400 Mbit/s realisiert werden. Für längere Übertragungsstrecken kann dieser Ansatz kostengünstig um Signalverstärker und verlustarme Impedanz angepasste Datenkabel erweitert werden oder aber auch durch eine multi-mode Glasfaserverbindung.